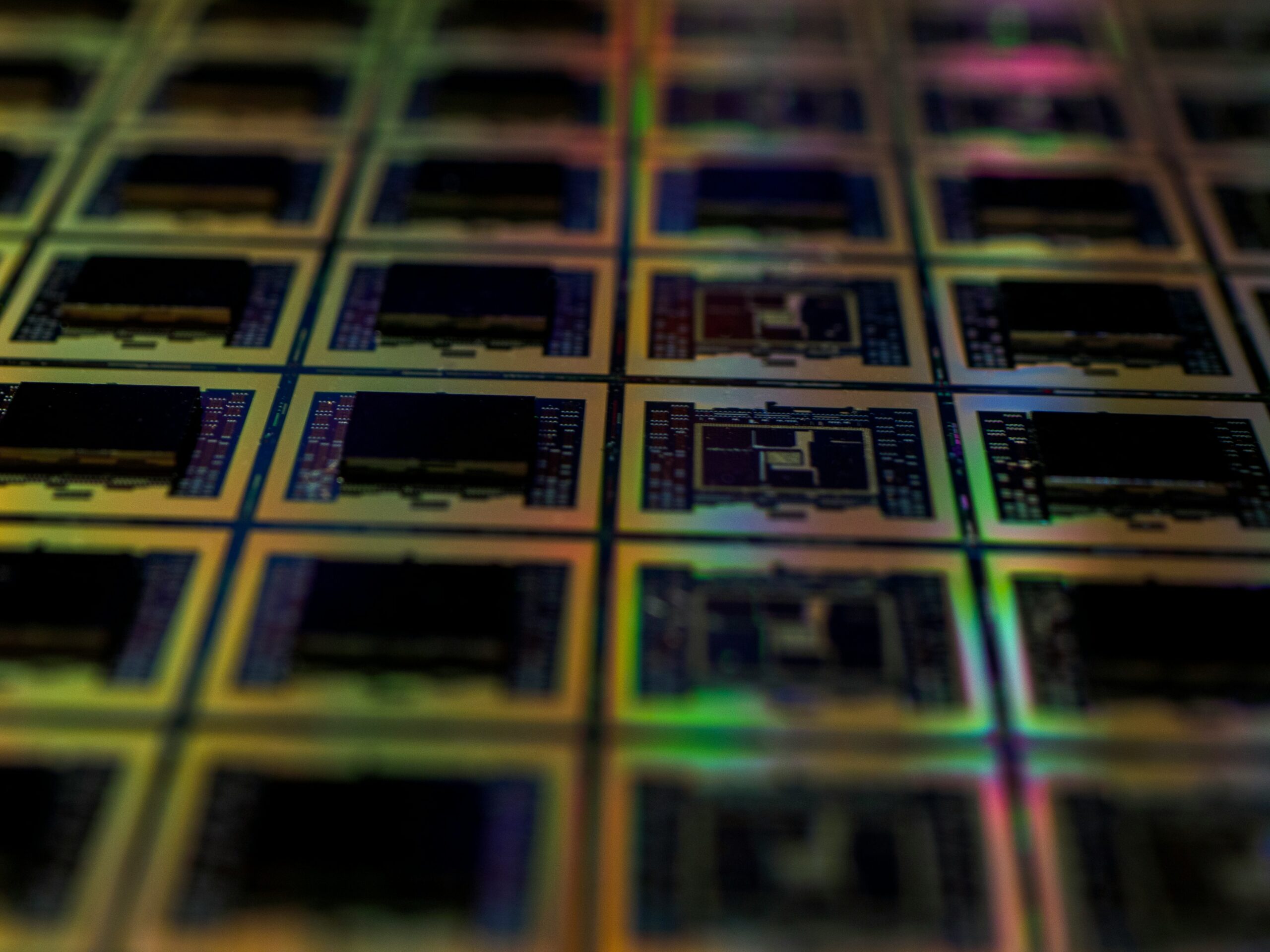

TSMC は、台湾・高雄の Fab 22 において、2 nm プロセス(N2)の初期ウェハ露光を成功させ、量産化に向けた重要なマイルストーンを通過した。N2 の商用化は 2025 年後半~ 2026 年を見据えており、半導体業界にとって転換期となる節目だ。

Fab 22 での初露光成功:N2 技術の初歩段階が始動

高雄にある Fab 22 にて、TSMC は初の 2nm プロセス ウェハ露光を達成した。これは N2 リスク試作段階から次の段階へ移行する象徴的な成果である。設備・プロセス間の整合性確認やマスク整備、露光装置の調整といった技術課題のうち、露光段階の第一歩をクリアした。

この成果をもって、TSMC は 2025 年の後半からの量産化(HVM:High Volume Manufacturing)開始に備えるフェーズへ移行する可能性が高まった。

N2 プロセスの特徴と先端技術要素

N2 プロセスは、TSMC にとって最初のナノシート(Gate-All-Around/GAA)型トランジスタ採用ノードである。従来の FinFET 構造からの転換を伴うアーキテクチャ移行が要となる技術革新だ。

N2 技術における注目点は以下の通り:

- トランジスタ密度の向上

- 消費電力削減と性能強化のトレードオフ改善

- 裏面給電(Backside Power Delivery)や電源・配線最適化

- 欠陥密度(defect density)の抑制と歩留まり改善

これらを制御できて初めて、N2 量産は実効フェーズへ移行できる。

顧客予約と初期採用動向

TSMC は N2 技術に対して多数の顧客を確保しているとされ、Intel、AMD、MediaTek などが早期採用の候補に挙げられている。

たとえば、AMD は N2 プロセスでの初製品シリコンを確認したと発表しており、サーバー/HPC 分野での製品化を視野に入れている。

また、MediaTek は N2P(2 nm 派生プロセス)を利用した次世代 SoC をすでに設計しており、2026 年後半の量産化を目指す計画を打ち出している。

Apple も TSMC の 2nm 容量を大口予約したという報道があり、同社の次世代 A/M 系プロセッサ投入を想定した動きと見られる。

量産化スケジュールとリスク要因

現時点では、量産化は 2025 年後半~ 2026 年初頭が目標とされている。だが、実際に「量産レベルの歩留まり」で供給可能となるには、まだ多くの技術的課題が残る。

主なリスク要因は以下である:

- 欠陥密度制御と歩留まりの安定化

- 製品設計最適化(設計ルール・セルライブラリの成熟)

- 装置キャリブレーションと歩留まり成長速度

- 顧客要求分野(高性能/低消費電力/AI 需要など)との整合性

- 供給・材料制約、工場設備稼働率

これらの要素がうまく揃わなければ、量産化のロールアウトが遅延する可能性もある。

意義:半導体の世代転換期

TSMC の N2 の量産化は、業界にとって大きな節目である。N2 が商用化すれば、3 nm 世代に対して性能・消費電力・密度の改善幅がさらに拡大し、AI・モバイル・サーバー市場におけるチップ競争を再構築する契機となる。

また、N2 技術の実用化成功は、今後の 1.4nm や派生プロセス(N2P、N2X など)への段階的移行を加速させる可能性がある。

ただし、「最初に量産できる」技術と「安定供給できる」技術は別物である。今後の歩留まり改善、顧客適用範囲拡大、供給体制強化の進捗を注視する必要がある。